# CMM-54415

# Application Module for Freescale MCF54415 MCU

Hardware User Manual

Axiom Manufacturing • 1226 Exchange Drive • Richardson, TX 75081

Email: <u>Sales@axman.com</u> Web: <u>http://www.axman.com</u>

#### CONTENTS

| CAUTIONARY NOTES                  |

|-----------------------------------|

| TERMINOLOGY                       |

| SUPPORTING DOCUMENTATION          |

| FEATURES                          |

| GETTING STARTED                   |

| CMM-54451 OPTION SETTINGS         |

| CMM OPTION AND CONNECTOR LOCATION |

| CMM-54415 STARTUP                 |

| SOFTWARE DEVELOPMENT              |

| CMM-54415 HARDWARE AND OPTIONS    |

| POWER SUPPLY                      |

| J7 - Power Jack                   |

| RESET INDICATION AND SWITCH       |

| INDICATORS                        |

| SW2 Switch                        |

| System Clock References           |

| Мемогу 10                         |

| COMMUNICATION PORTS               |

| J6 10/100TX ETHERNET PORT         |

| J5 RS232 COM Port                 |

| J8 CAN or RS485 Port              |

| J8 CONNECTION                     |

| J3 BDM DEVELOPMENT PORT           |

| Figure1 – BDM Cable Connection    |

| JP2 - BDM_EN OPTION               |

| J3 Port Connection                |

| I/O CONNECTORS                    |

| J1 - MCU_PORT                     |

|                                   |

| J4 - GPIO_PORT                    |

| TROUBLESHOOTING                   |

## **Cautionary Notes**

- 1) Electrostatic Discharge (ESD) prevention measures should be applied whenever handling this product. ESD damage is not a warranty repair item.

- 2) Axiom Manufacturing reserves the right to make changes without further notice to any products to improve reliability, function or design. Axiom Manufacturing does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under patent rights or the rights of others.

- 3) EMC Information on the CMM-54415 board:

- a) This product has not been tested for requirements of CE and the FCC emissions and immunity.

- b) This product is designed and intended for use as a development platform for hardware or software in an educational / professional laboratory or as a component in a larger system.

- c) In a domestic environment this product may cause radio interference in which case the user may be required to take adequate prevention measures.

- d) Attaching additional wiring to this product or modifying the products operation from the factory default as shipped may affect its performance and also cause interference with other apparatus in the immediate vicinity. If such interference is detected, suitable mitigating measures should be taken.

# Terminology

This development board applies option selection jumpers. Terminology for application of the option jumpers is as follows:

Jumper on, in, or installed = jumper is a plastic shunt that fits across 2 pins and the shunt is installed so that the 2 pins are connected with the shunt.

Jumper off, out, or idle = jumper or shunt is installed so that only 1 pin holds the shunt, no 2 pins are connected, or jumper is removed. It is recommended that the jumpers be placed idle by installing on 1 pin so they will not be lost.

This development board applies CT (cut trace) or option selections that require a soldering tool to install or remove. This type connection places an equivalent Jumper Installed type option. Applying the connection can be performed by installing a 0 ohm resistor component or small wire between the option pads. See the Options section for more details.

# **Supporting Documentation**

- MCF54415 Reference Manual, Freecale Semiconductor, <u>www.freescale.com</u>

- MCF54415 Data Sheet, Freescale semiconductor.

- MQX RTOS Reference, Freescale Semiconductor

- Codewarrior for Coldfire, Freescale Semiconductor

- CMM-54415\_Schematic\_Rev-B.pdf, Axiom Manufacturing

Support Link: http://www.axman.com/support/CMM-54415/

# **FEATURES**

The CMM-54415-OEM is a module featuring the MCF54415 micro-controller. This small form factor (2.20"X3.5") board is ideal for industrial OEM embedded application where low cost and small size are important.

FEATURES with Module support:

- MCF54415 MCU, 256 MAPBGA Package

- 32 bit w/ EMAC and MMU support

- 250Mhz operation

- 64K Byte single cycle SRAM

- DDR, DDR2, Mobile DDR Controller

- 10/100 Ethernet with IEEE 1588 support

- 32 bit Data and Address Bus

- 4x SPI Serial ports

- 2x I2C Serial Ports

- 10x UART Serial Ports

- 5x Interrupt Inputs

- 4x PIT timers

- 4x 32 bit Timers w/ DMA

- 12 bit dual ADC, 8 channels

- 8 channel PWM Timers

- RTC clock with back-up option

- BDM / JTAG Port

- Internal Oscillator w/ PLL clocking

- 3.3V / 1.2V operation

- 128MByte DDR2 memory

- 64M Byte 32 bit Parallel flash memory

- ◆ 10/100TX Ethernet Port with RJ45 connector

- RESET and ABORT (IRQ7) push switches

- ◆ 25MHz Primary and 32Khz RTC Oscillators

- COM Port (UART0), IDE pin header w/ DSUB-9

- CAN / 485 Port (CAN / UART9), 3 pin .1 inch friction lock

- ◆ MCU I/O Port, 2 x 25 pins, .1 inch grid \*\*

- MCU Bus Port (64K x 8 bit), 2 x 17 pins, .1 inch grid\*\*

- BDM / JTAG Port, 26-pin Freescale standard

- Regulated +3.3V / 1.8V / 1.2V power supplies w/ indicator

- Board support package and Freescale MQX RTOS port

- Cables and Wall-Plug power optional

#### **Specifications:**

Power Input: 2.1mm DC plug, +6 to +30VDC, 12VDC @ 120ma typical. Board Size: 2.2 W x 3.5 L x 0.6 H Inches

Options: CAN Bus or RS485 transceiver interface is a build option. \*\* = not populated, build option

The CMM-54415 is provided with a Boot loader flashing utility installed and operating a MQX RTOS test application. Boot loader application allows the user to flash program the board with a new MQX RTOS application object code file (S record). The boot loader utility correctly maps MQX file into the on board flash memory so that it will load from flash into the DDR memory and execute. A RS232 COM port serial interface to a PC host is applied for the boot loader.

# **GETTING STARTED**

The CMM-54415 is provided with a Boot loader flashing utility installed and operating a MQX RTOS test application. Boot loader application allows the user to flash program the board with a new MQX RTOS application object code file (S record). The boot loader utility correctly maps MQX file into the on board flash memory so that it will load from flash into the DDR memory and execute. A RS232 COM port serial interface to a PC host is applied for the boot loader.

Development board users should also be familiar with the hardware and software operation of the target MCF54415 device, refer to the Freescale User Guide for the device and the Coldfire V4 Reference Manuals for CPU operation details. The development board purpose is to assist the user in quickly developing an application with a known working environment, to provide an evaluation platform, or as a control module for an applied system. Users should be familiar with memory mapping, memory types, and embedded software design for the quickest successful application development.

# **CMM-54451 Option Settings**

| OPTION     | Installed                            | Open / Idle                                     |

|------------|--------------------------------------|-------------------------------------------------|

| JP1 - RXD  | UART0 RXD connected to COM port      | UARTO RXD not applied by COM port               |

| JP1 - RTS  | UARTO RTS COM flow control           | UARTO RTS not applied by COM port               |

| JP1 – CTS  | UARTO CTS COM flow control           | UART0 CTS not applied by COM port               |

| JP1 - CAN  | UART9 / CAN1 RXD applied to J8       | UART9 / CAN1 RXD not applied                    |

| JP1 – PRG  | Bootloader Enabled at RESET          | User Application enabled at Reset               |

| JP2 – JTAG | Selects BDM mode for the J3 BDM      | Selects JTAG Mode on the J3 BDM port.           |

|            | Port. (default)                      |                                                 |

| JP3 – GPIO | Enables Port H GPIO operation on J4  | J3 GPIO Port pins 1 to 4 are Analog input only. |

|            | GPIO port pins 1 to 4.               |                                                 |

| JP4 – GPIO | Enables Port G / H GPIO operation on | J3 GPIO Port pins 5 to 8 are Analog input only. |

|            | J4 GPIO port pins 5 to 8.            |                                                 |

Option jumpers are applied on the CMM-54415 board for hardware settings.

Note: See I/O Port descriptions for further details on signal options.

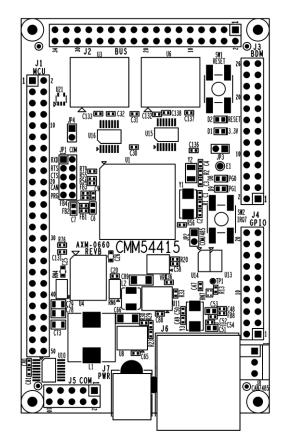

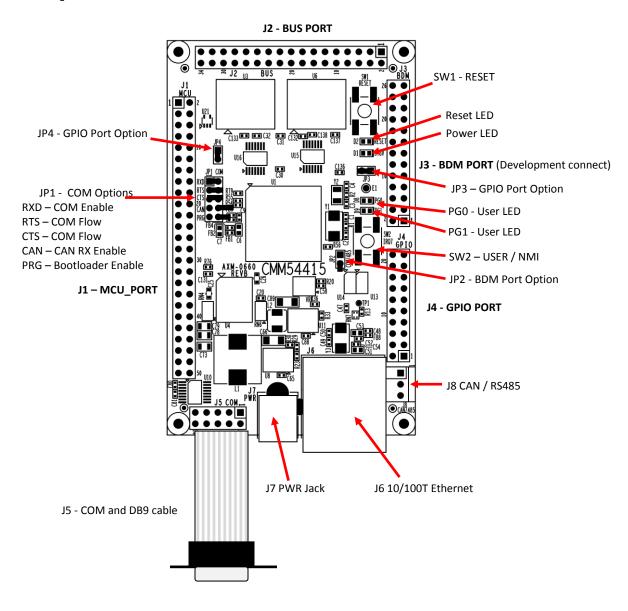

#### **CMM Option and Connector Location**

# CMM-54415 Startup

Follow these steps to connect and power on the CMM for the default Boot Loader prompt or MQX RTOS example operation:

- 1) Carefully unpack the CMM-54415 and observe ESD preventive measures while handling the development board.

- 2) Apply a serial terminal software on the host PC. Download and install TERA TERM or another serial terminal type software if required for COM port terminal communication.

- 3) Apply COM port cable to the CMM board DB9 connector. Host PC may apply COM port or a USB COM port cable to provide the connection.

- 4) Configure terminal software for COM port number and 115.2K baud, 8 data, 1 stop, no parity connection type.

#### CMM-54415 USER MANUAL V1.0

- 5) Verify that the JP1 PRG jumper option is installed on both pins.

- 6) Apply 9 or 12VDC to the CMM board power jack and the board will prompt on the serial port.

CMM-54415 will send the Boot loader prompt on the serial COM port with the PRG option installed at RESET:

Main Menu R) Flash Erase F) Firmware Upload P) Parameters Upload M) Memory Tools

T) Test

e) Exit

Select:

- 7) Typing keys on the host PC keyboard may select the menu options. See Boot Loader chapter for more detail.

- 8) Apply a Ethernet cable between the Host PC and the CMM board. A Ethernet switch may be in the path.

- 9) Remove the CMM board JP1 PRG option and press the RESET switch then release.

- 10)The CMM board prompt will indicate launching of the loaded application. The demo MQX application prompt is provided here for reference:

Initializing DDR..DDR Initialized. Testing DDR..passed ok Writing 0xFFFFFFF to 0x40000000.. passed ok Writing 8-bit values to 0x40100000.. copying..... go 4010221a Starting http server No.0 on IP 192.168.1.129...[OK]

Shell (build: Jan 29 2015) Copyright (c) 2013 Freescale Semiconductor; shell>

11)Launching web browser software on the Host PC and typing http://192.168.1.129 into the address will present the CMM board demo web page. If web page is not found, please check for network issues such as duplicate IP address or limited IP access if a network router is located on the local network. Host PC may also have security settings to prevent IP access.

The CMM board is ready to develop an application now.

### Software Development

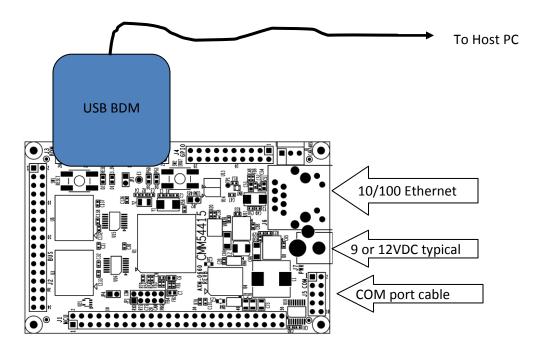

Several RTOS and C compilers are available for the Coldfire V4 and all will support generating applications for this board. Typical development is assisted by a Development Cable connection to the BDM Port on the board from a host PC operating supporting development interface software (IDE). Codewarrior supports the PE Micro cables and others.

The example Board Support Package (BSP) is provided as a MQX RTOS example applied with Codewarrior. User starting with the BSP may add applications with minimal additional hardware interfacing required. Initialization, Ethernet, UART (COM Port), and GPIO operations are provided example application.

The typical development environment applies the CMM board DDR ram memory as the application memory space. After the user application is completed in the development environment, the application may be loaded by the Boot Loader (S record load) into the CMM board flash memory and the application will run on a Reset or power cycle.

Programming the CMM board from the development environment for DDR memory space operation is problematic and the Boot loader should be applied. For applications that will boot and operate from the flash memory space on the CMM board, the Codewarrior flash programmer may be applied.

# **CMM-54415 Hardware and Options**

The CMM-54415 board provides an application or development platform for the MCF54415 microcontroller. Operating mode of the MCF54415 is set at RESET for Master Mode, 32 bit Flexbus bus with 32 bit boot device (flash) and crystal oscillator of 25Mhz. Following are descriptions of the main components and options provided on the board.

### **POWER SUPPLY**

Input power is applied by external connection to the J7 PWR power jack or J4 GPIO port pin 20. The input supply is provided to the 3.3V regulator U8 and to the 1.8V regulator U11. VR1 provides 1.2V core voltage to the MCF54415 device. The DDR2 ram memory is provided 0.9V termination voltage by U9.

With a +5VDC to +26VDC potential applied for input, the +3.3V indicator should be ON.

#### J7 - Power Jack

J7 provides the default power input to the board. The power jack accepts a standard  $2.0 \sim 2.1$ mm center barrel plug connector (positive voltage center) to provide the +VIN supply of +5 to +26 VDC (+9VDC typical).

### **RESET Indication and Switch**

Reset operation is provided by SW1 RESET switch, LV1 low voltage detector, J3 BDM Port operation, or user applied connection to the RESET\* signal on the J1 MCU PORT. If the main 3.3V supply is below operating level, the LV1 voltage detector will cause the MCF54415 to stay in the RESET condition. SW1 RESET switch provides for manual application of the MCF54415 RESET\* signal. Both the RESET switch and LV1 provide a 150ms delay after release for the system to stabilize.

Application of RESET will cause the Bootloader or user application to initialize the MCF54415. Previous DDR2 memory content and operating state of the MCF54415 will be lost.

The RESET indicator is ON during the Reset condition. The CMM board will not operate if the RESET indicator is ON.

### **INDICATORS**

Indication is provided for power supply status, CPU Reset status, Ethernet status, and User application. The indications may be applied to determine proper operation of the development board. The Ethernet status indicators may be configured by PHY management interface to indicate other status by user application, see the KSZ8041 data sheet and MCF54451 Management port for details.

| Indicator | Summary |

|-----------|---------|

|-----------|---------|

| INDICATOR | Location | COLOR  | OPERATION                                                     |

|-----------|----------|--------|---------------------------------------------------------------|

| +3.3V     | Board    | Green  | +3.3V power present when ON.                                  |

| RESET     | Board    | RED    | CPU is in RESET state when ON                                 |

| LNK / ACT | J6       | Green  | Ethernet has Link, Blinks with activity.                      |

| SPD       | J6       | Yellow | Ethernet is operating 100 base when ON, 10 Base off with Link |

| PG0 / D8  | Board    | Green  | User application, port PG0 = 0 = ON.                          |

| PG1 / D9  | Board    | Green  | User application, port PG1 = 0 = ON.                          |

### SW2 Switch

SW2 provides user application feature if applied. The switch is active low and operates the IRQ7 / NMI interrupt if so enabled by the application. The JP1 - PRG option is in parallel with the switch and will prevent switch application operation if installed. Pressing SW@ during the RESET condition will launch the Boot loader by default.

### System Clock References

The reference oscillator is a 25MHz crystal. MCF54415 clock is generated by the internal PLL from the reference for default system frequency of 250MHz. User applications may change the clock setting to a lower frequency under software control.

The RTC reference clock is 32.768Mhz. The RTC (Real Time Clock) may be applied for time keeping and monitoring applications. The MCF54415 applies this clock internally.

### Memory

Memory banks of 128M byte DDR2 Ram and 64M byte Flash are provided on the CMM board. The MCF54415 provides 64K bytes of SRAM memory and 8K byte cache Ram internally.

The MCF54451 boots by default from the flash memory bank on the CMM board. Subsequent application operation typically initializes the DDR2 memory, transfers application from the flash to the DDR2, and then transfers program operation to the DDR2 memory for highest speed operation.

Flash Type: 2x Spansion S29GL256P devices as 32 bit wide data on CS0 select.

DDR2 Ram type: Alliance AS4C128M8D2 industrial temperature.

Note: The MCF54415 DRAM controller must be configured prior to application of the memory space when development tools are applied.

### **Communication Ports**

The CMM-54415 provides J6 10/100T Ethernet Port, J5 RS232 Serial COM Port, and optional J8 RS485 or CAN Port on board. User may apply up to 8 UARTs, I2C, SPI, SOM, and CAN off board with hardware expansion.

### J6 10/100TX Ethernet Port

J6 provides the Ethernet physical interface connection for the MCF54415 Media Access Controller (MAC). A Micrel KSZ804110/100T physical layer transceiver (PHY) provides the signal translation for Ethernet application. (FEC/MAC). A complete IEEE802.3 interface with IEEE1588 Precision Time support is provided. Features include HP auto MDII connection and 2 jack located status indicators.

#### J6 Ethernet Status Indicators

| LNK ACT | Green  | Ethernet has Link and will blink with activity                    |

|---------|--------|-------------------------------------------------------------------|

| SPD     | Yellow | Ethernet link is operating 100T base when on, 10TX Base when off. |

Note: Ethernet port must be operating for status indications.

The LED indication and PHY configuration may be modified by the MAC management port operation of the PHY device.

MCF54415 software application must operate the Ethernet port for communication. The PHY will indicate network connection without MCF54415 data transfer.

### J5 RS232 COM Port

The J5 COM port provides a 10 pin ribbon connection for a standard socket type 9 pin serial connector. The port provides RS232 type interface to the MCF54415 UART0 peripheral. COM port is applied by the Boot Loader monitor at 115.2K baud default. Following is connection reference:

J5

| DB9-1            | 1 | 2  | DB9-6            | The <b>COM</b> port is a DB9 socket connector with RS232                                                   |  |

|------------------|---|----|------------------|------------------------------------------------------------------------------------------------------------|--|

| DB9-2 <b>TXD</b> | 3 | 4  | <b>CTS</b> DB9-7 | signal levels.                                                                                             |  |

| DB9-3 <b>RXD</b> | 5 | 6  | <b>RTS</b> DB9-8 | <b>CTS / RTS</b> are enabled by JP1 options RTS and CTS to MCF54415 signals RTS0 and CTS0 respectfully for |  |

| DB9-4            | 7 | 8  | DB9-9            | UART0 hardware flow control.                                                                               |  |

| DB9-5 GND        | 9 | 10 | N/C              | 1,4,6 connected for status null to host                                                                    |  |

The 1, 4, 6 and 9 pins provide RS232 status signals

#### JP1 RTS and CTS Options

Install the RTS and CTS option jumpers on both header pins to connect the signals to the MCF54415 controller. Application software will need to support the flow control signal operation provided by these pins.

### J8 CAN or RS485 Port

J8 is a build option to provide a CAN network port or a RS485 compliant network port. The CAN application is supported by a CAN1 controller in the MCF54415. RS485 operation is provided by UART9 connection to the MCF54415 on the same I/O pins. User application software must configure the pins and operate the CAN controller or UART 9 for port operation.

The CAN transceiver is set to fast slew rate signal drive for up to 1M baud transfer rate. Termination is DC 120 ohms. The 485\_CTL signal operated by MCF54415 port PK7 may disable the CAN transceiver output with a high level applied.

The RS485 transceiver is provided a 100 ohm AC termination. 485 requires the transmit operation to be enabled by a high level on the 485\_CTL signal on MCF54415 port pin PK7. Reception is with the same pin in the low (default) state.

#### **J8** Connection

The port connector accepts standard .1 inch space .025 square pin socket connectors and provides a friction lock to retain the cable connector.

| J8 Pin | Signal                 |  |  |  |  |  |  |

|--------|------------------------|--|--|--|--|--|--|

| 1      | CAN Low or 485 A       |  |  |  |  |  |  |

| 2      | CAN High or 485 B      |  |  |  |  |  |  |

| 3      | Ground / Signal Common |  |  |  |  |  |  |

### **J3 BDM Development Port**

The BDM development port provides standard Coldfire development connection as defined by Freescale Semiconductor. The port operates in one of two modes determined at RESET, BDM Mode or JTAG Mode. Default mode of operation is BDM for development.

#### Figure1 – BDM Cable Connection

#### JP2 - BDM\_EN Option

The BDM\_EN option jumper must be installed to operate the PE Coldfire cable or any similar BDM type development cable. Cable will not connect to the MCF54415 without this jumper installed. Jumper should be removed during application mode operation to reduce emissions from the CMM board.

JP2 Installed = BDM\_PORT is in BDM Mode (Development mode = BDM).

JP2 Open / Idle = BDM\_PORT is in JTAG Mode (Development mode = JTAG).

#### **J3 Port Connection**

**BDM /JTAG Port Connection**

|        | 1  | 2  | BKPT*  |

|--------|----|----|--------|

| GND    | 3  | 4  | DSCLK  |

| GND    | 5  | 6  | TCLK   |

| RESET* | 7  | 8  | DSI    |

| +3.3V  | 9  | 10 | DSO    |

| GND    | 11 | 12 | PST3   |

| PST2   | 13 | 14 | PST1   |

| PST0   | 15 | 16 | DDATA3 |

| DDATA2 | 17 | 18 | DDATA1 |

| DDATA0 | 19 | 20 | GND    |

|        | 21 | 22 |        |

| GND    | 23 | 24 | TCLK   |

| +1.5V  | 25 | 26 | TA*    |

|        |    |    |        |

# **I/O Connectors**

### J1 - MCU\_PORT

The MCU PORT provides access to the MCF54415 General Purpose I/O ports. Ports typically have several available peripheral functions configurable by user application.

| PB2 / UART8_TX / CAN0_TXD / I2C0_SCL             | 1  | 2  | I2C0_SDA / CAN0_RXD / UART8_RX / PB1             |

|--------------------------------------------------|----|----|--------------------------------------------------|

| PH7 / SIM_VEN / I2C2_SDA / SSI0_RXD              | 3  | 4  | FB_CLKOUT / PB7                                  |

| (Input) RESET*                                   | 5  | 6  | RESETOUT* (Output)                               |

| PH6 / SIM_DATA / I2C2_SCL / SSI0_TXD             | 7  | 8  | SSIO_FS / SIM_RST / UART7_TX / PH5               |

| PA0 / FB_TSIZ0 / FB_WE0 / FB_BE0                 | 9  | 10 | FB_ALE / PA7                                     |

| PA1/ FB_TSIZ1 / FB_WE1 / FB_BE1                  | 11 | 12 | SSI0_MCLK / SSI_CLKIN / SIM_CLK / PH4            |

| PH3 / UART7_RX / SIM_PD / SSIO_BCLK              | 13 | 14 | FB_CS5* / PB6                                    |

| PB5 / FB_CS4*                                    | 15 | 16 | FB_BE3 / FB_WE3 / FB_CS3* / PA3                  |

| PA2 / FB_WE2 / FB_BE2 / FB_CS2*                  | 17 | 18 | FB_CS1* / PB4                                    |

| PD2 / RGPIO1 / PWM_EXT_A3 / TIM3_I/O             | 19 | 20 | UART0_CTS / UART4_TX / RGPIO5 / PF6              |

| PD1 / SDHC_DAT2 / RGPIO2 / PWM_EXT_A2 / TIM2_I/O | 21 | 22 | UART0_RTS / UART4_RX / RGPIO6 / PF5              |

| PD0 / SDHC_DAT1 / RGPIO3 / PWM_EXT_A1 / TIM1_I/O | 23 | 24 | UART2_CTS / UART6_TX / RGPIO14 / SSI1_BCLK / PE6 |

| PE7 / RGPIO4 / PWM_EXT_A0 / TIM0_I/O             | 25 | 26 | UART2_RTS / UART6_RX / RGPIO15 / SSI1_FS / PE5   |

| PE3 / SSI1_TXD / PWM_B3 / UART2_TX               | 27 | 28 | UART2_RX / PWM_A3 / SSI1_RXD / PE4               |

| PE2 / RGPIO7 / DSPI3_SCK / UART5_TX / UART1_CTS  | 29 | 30 | UART1_RTS / UART5_RX / RGPIO8 / DSPI3_PCS0 / PE1 |

| PF7 / DSPI3_SOUT / I2C5_SCL / UART1_TX           | 31 | 32 | UART1_RX / I2C5_SDA / DSPI3_SIN / PE0            |

| PC7 / I2C1_SDA / UART9_RX / CAN1_RXD             | 33 | 34 | CAN1_TXD / UART9_TX / I2C1_SCL                   |

| PC0 / DSPI0_PCS1                                 | 35 | 36 | DSPI0_PCS0 / I2C3_SDA / SDHC_DAT3 / PD7          |

| PD6 / SDHC_CLK / I2C3_SCL / DSPI0_SCK            | 37 | 38 | DSPI0_SIN / UART3_RX / SDHC_CMD / PD5            |

| PD4 / UART3_TX / SDHC_DAT0 / DSPI0_SOUT          | 39 | 40 | IRQ7* / PC6                                      |

| PC5 / IRQ6*                                      | 41 | 42 | OW_DAT / RGPIO0 / DACK0*                         |

| PC4 / IRQ4*                                      | 43 | 44 | IRQ3* / DSPI0_PCS3 / PC3                         |

| PC2 / DSPI_PCS2 / IRQ2*                          | 45 | 46 | IRQ1* / PC1                                      |

| GND                                              | 47 | 48 | +3.3V                                            |

| CAN_HI / 485_A                                   | 49 | 50 | CAN_LO / 485_B                                   |

### J 2 - BUS\_PORT

The BUS PORT provides 64K Byte access space with 3 selects to peripherals. All signals on the BUS PORT have a peripheral connection on the CMM-54415 board. Application of the BUS signals will require the addition of buffers on the external connections, ribbon cables should not be applied.

| FB_D24                 | 12    | FB_D25        |

|------------------------|-------|---------------|

| FB_D26                 | 34    | FB_D27        |

| FB_D28                 | 56    | FB_D29        |

| FB_D30                 | 78    | FB_D31        |

| L_A0                   | 9 10  | L_A1          |

| L_A2                   | 11 12 | L_A3          |

| L_A4                   | 13 14 | L_A5          |

| L_A6                   | 15 16 | L_A7          |

| L_A8                   | 17 18 | L_A9          |

| L_A10                  | 19 20 | L_A11         |

| L_A12                  | 21 22 | L_A13         |

| L_A14                  | 23 24 | L_A15         |

| PB4 / FB_CS1*          | 25 26 | FBCS4* / PB5  |

| PB6 / FB_CS5*          | 27 28 | FB_OE* / PA6  |

| PA3 / FB_WE0* / FB_BE0 | 29 30 | FB_R/W* / PA5 |

| FB_ALE                 | 31 32 | FB_TA* / PA4  |

| +3.3V                  | 33 34 | GND           |

|                        |       | ]             |

### J4 - GPIO\_PORT

The GPIO PORT provides access to the MCF54415 Analog and PWM timer signals. Option jumpers JP2 and JP4 provide port signal options for the analog signals. The JP3 and JP4 options installed allow the optional digital input and output to be connected to connector pins with the analog signal.

| Option signal         | Default Analog<br>Signal |    | pin                | Default Analog<br>Signal | Option signal         |

|-----------------------|--------------------------|----|--------------------|--------------------------|-----------------------|

| JP                    | 3 SIGNAL OPTIONS         |    |                    | JP4 SIGNAL OPTIONS       |                       |

| (MCU Port pin 3) PH7  | ADC_IN0                  | 1  | 2                  | ADC_IN1                  | PH6 (MCU Port pin 7)  |

| (MCU Port pin 8) PH5  | ADC_IN2                  | 3  | 4                  | ADC_IN3 / DAC0           | PH3 (MCU Port pin 13) |

| (MCU Port pin 12) PH4 | ADC_IN4                  | 5  | 6                  | ADC_IN5                  | PG2                   |

| PWM_FAULT2 / PG4      | ADC_IN6                  | 7  | 8                  | ADC_IN7 / DAC1           | PD3 (MCU Port pin 42) |

| F                     | 9                        | 10 | PG1 / PWM_SYNC     |                          |                       |

| SDHC1_DAT1 / DSPI1_S0 | CK / PWM_A0 / PG5        | 11 | 12                 | PF2 / PWM_A1 / DSPI      | 1_PSC0 / SDHC_DAT3    |

| SDHC_DAT1 / DSPI1_PC  | 13                       | 14 | PG6 / PWM_B0 / DSP | I1_SIN / SDHC_DAT2       |                       |

| SDHC_DAT2 / DSPI1_PC  | 15                       | 16 | PG7 / PWM_B2 / DSP | 1_SOUT / SDHC_DAT0       |                       |

| F                     | PWM_FAULT0 / PG3         |    |                    |                          |                       |

|                       | 19                       | 20 | +VIN               |                          |                       |

# TROUBLESHOOTING

The CMM-54415 is fully tested and operational before shipping. If it fails to function properly, inspect the board for obvious physical damage first. Verify the communications setup as described under GETTING STARTED.

The most common problems are improperly configured options or communications parameters.

- 1. Verify default option settings and RESET the board. The CFG option installed should always provide the Boot loader prompt.

- 2. Wait 20 seconds for a prompt. If Ethernet cable is not applied, MQX applications may be waiting for Ethernet connection but will time out and typically provide a prompt.

- 3. Make sure that the RESET\* line is not being held low or the RESET indicator is not on constantly.

- 4. Verify that your COM communications port is working by substituting a known good serial device or by doing a loop back diagnostic. Make sure the terminal software is set correctly.

- 5. Verify the power source, +3.3V Indicator is ON? You should measure a minimum of 9 volts between the GND and +VIN (GND Test Point and J4 GPIO Port pin 20) with the standard power supply provided.

- 6. If no power indications or voltage is found, verify the wall plug connections to AC outlet and the PWR jack power connector.

- 7. Disconnect all external connections to the board except for COM to the PC and the wall plug and check operation again.

- 8. Contact <u>support@axman.com</u> by email for further assistance. Provide board name and describe problem.